Cadence has unveiled what it describes as the world’s first agentic AI workflow for front-end silicon design and verification, introducing the ChipStack AI Super Agent as a major step toward autonomous chip development.

The announcement marks a significant moment for the semiconductor industry, where escalating design complexity, shrinking time-to-market windows and a shortage of experienced engineering talent have placed unprecedented pressure on verification and front-end workflows.

According to Cadence, the new ChipStack AI Super Agent can deliver up to 10X productivity improvements across key design and verification tasks — from coding RTL and testbenches to generating test plans, orchestrating regression testing, debugging and even automatically fixing identified issues.

From AI assistance to agentic workflows

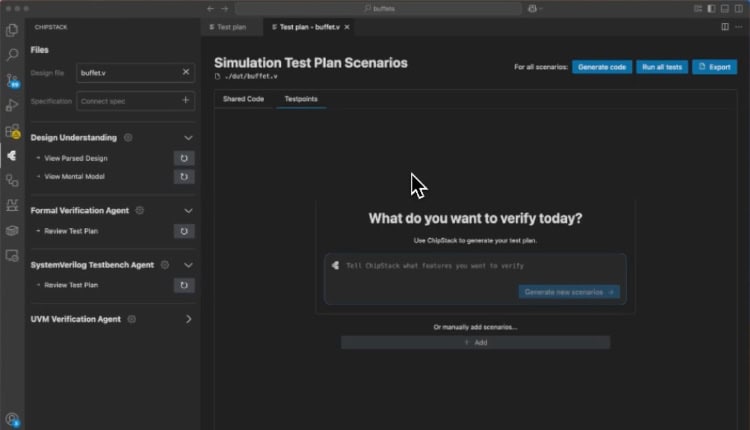

Unlike traditional AI copilots that assist engineers in discrete tasks, the ChipStack AI Super Agent is designed to orchestrate an entire workflow autonomously. It deploys multiple “virtual engineers” that operate across Cadence’s electronic design automation (EDA) stack, calling underlying tools and coordinating complex processes without constant human intervention.

“ChipStack represents a major leap in our design-for-AI and AI-for-design strategy, applying agentic AI directly to our customers’ front-end flows to tackle the growing complexity and scale of modern chips,” said Anirudh Devgan, president and CEO of Cadence. “By leveraging intelligent agents that autonomously call our underlying tools, we are enabling dramatic productivity gains for our customers in critical design and verification tasks while freeing scarce engineering talent to focus on innovation.”

The solution builds on Cadence’s broader Intelligent System Design strategy, combining AI orchestration with simulation and accelerated computing. It integrates with established Cadence platforms including the Verisium Verification Platform, Cadence Cerebrus Intelligent Chip Explorer and the JedAI data and AI platform — technologies already used in over 1,000 tapeouts globally.

Flexible AI model support

ChipStack is designed to operate across both cloud-based and on-premises environments. It supports open models such as NVIDIA Nemotron, which can be customised using NVIDIA NeMo, alongside cloud-hosted models including OpenAI GPT.

This hybrid flexibility reflects the semiconductor industry’s varied infrastructure strategies, particularly among companies handling sensitive intellectual property that may prefer on-premises inference.

“Our customers are facing a significant senior deficit in the engineering talent needed to deliver on their product roadmaps,” said Paul Cunningham, vice president and general manager of Research and Development at Cadence. “Our ChipStack AI Super Agent is a game changer for design and verification productivity, and deployments are ramping fast.”

Early industry adoption

The ChipStack AI Super Agent is already in early deployment with several leading chip and system design companies, including Altera, NVIDIA, Qualcomm, and Tenstorrent.

At Altera, early results suggest significant gains. “The Cadence ChipStack AI Super Agent has significantly reduced our verification effort in some areas by approximately 10X, enabling our team to achieve closure much more swiftly and confidently,” said Arvind Vidyarthi, senior director of engineering at Altera. “By pairing an interactive, engineer-in-the-loop experience with Cadence’s advanced AI-driven verification technologies, we are realising step-function productivity gains and achieving deeper functional coverage on our most complex designs.”

For NVIDIA, the collaboration underscores how AI is reshaping chip design itself. “As semiconductor complexity continues to accelerate, AI has become essential to designing the next generation of chips,” said Timothy Costa, GM of Industrial and Computational Engineering at NVIDIA. He noted that innovations such as ChipStack’s automated formal test plan generation, combined with NVIDIA accelerated computing, can unlock new productivity levels for designers.

At Qualcomm, early evaluations have been encouraging. “Early results indicate strong, encouraging performance enhancements, and we look forward to realising the productivity gains,” said Paul Penzes, vice president of engineering at Qualcomm.

Meanwhile, Tenstorrent reported up to 4X reduction in verification time during a three-month evaluation across critical design blocks. “Running the agent on Tenstorrent hardware also demonstrated our ability to deliver the high-performance, on-prem inference needed for production-scale LLM workloads,” said Daniel Cummings, principal engineer of RISC-V Cores at Tenstorrent.

Toward the ‘silicon agent’

Cadence describes ChipStack as a step toward a broader vision of a “silicon agent” — an AI system capable of spanning multiple design disciplines and workflows required to deliver next-generation intelligent devices.

If the productivity gains reported in early deployments scale across the industry, agentic AI could fundamentally reshape how chips are designed and verified, shifting engineers from manual orchestration toward supervisory roles — and potentially redefining the economics and timelines of semiconductor innovation.